数字集成电路(6)棍棒图和欧拉路径

本文最后更新于:2022年10月19日 下午

本人《数字集成电路设计》课程笔记,老师为王仁平。

本文主要讲述如何画“棍棒图”和“欧拉路径”来优化复合逻辑门电路的版图设计。

第六章 CMOS组合逻辑门电路

5. 复合逻辑门的版图技术

在(5)4【静态CMOS】组合逻辑的优化重点讨论了复合逻辑门的尺寸优化

此处,重点讨论如何设计逻辑门的版图

指标如下:

- 性能好($RC$小)

- 占用面积小

1. 棍棒图

棍棒图已经在(1)第二章 版图基础 中有所提及

1. 特点

- 器件不标尺寸

- 注重相对位置和连接关系

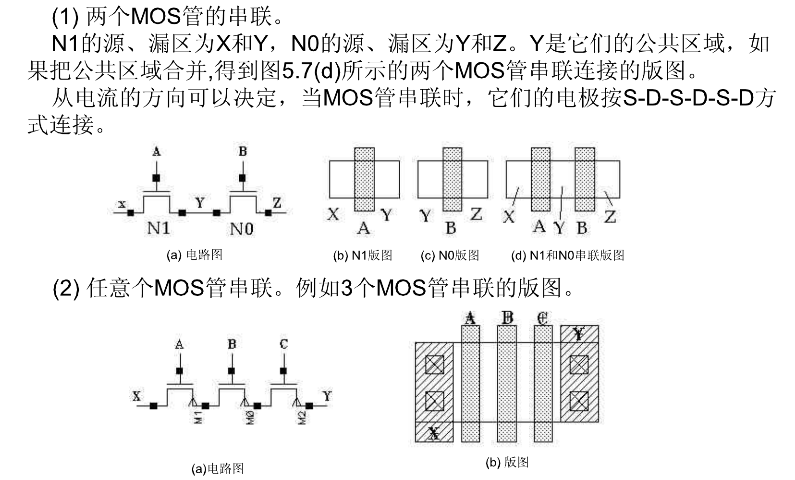

2. 串联-并联

串联:

并联:

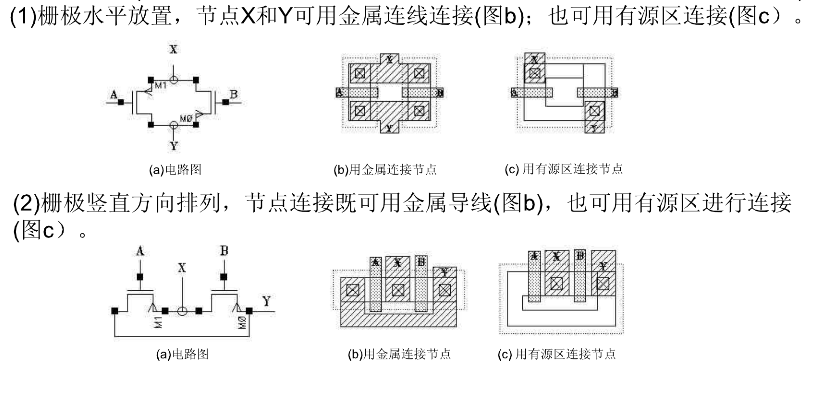

3. 好的棍棒图

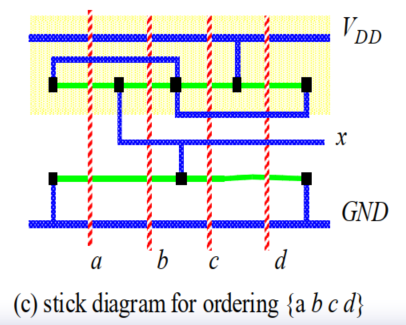

一个阱中只有一条扩散区

如上图,图中的扩散区被打断(图中圈画处)。根据设计规则,版图之间应该存在距离,使得版图面积增加。同时寄生参数也会增加。

改变输入端顺序,得到如下改进,

可以得到一个简单的结论:合理的输入端顺序可以优化版图——欧拉路径(见下文)

- 同一个输入控制的NMOS管和PMOS管对准。

2. 欧拉路径

根据欧拉路径可以得到合理的输入端排列顺序,使得复合逻辑门可以用连续的扩散区来实现,达到占用面积最小、性能好。

设计步骤步骤如下:

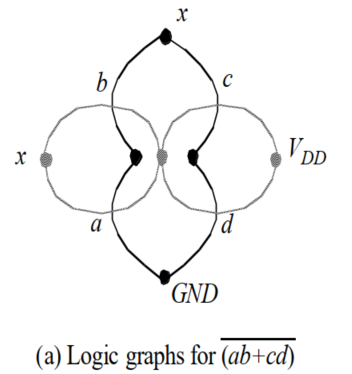

1. 构建逻辑图

逻辑图详见(4)2.3

此处不加赘述

2. 识别欧拉路径

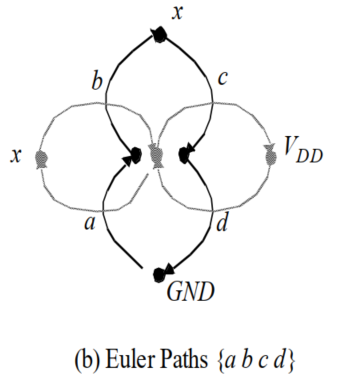

欧拉路径:通过逻辑图中所有节点并且每条边只经过一次的路径

- 如果上拉网络或者下拉网络存在欧拉路径,就说明多个晶体管可以共用一条扩散区。

- 如果上拉网络和下拉网络的欧拉路径相同,说明同一个输入控制的NMOS管和PMOS管对准

- 欧拉路径的顺序,就是输入端在版图中的排列顺序。

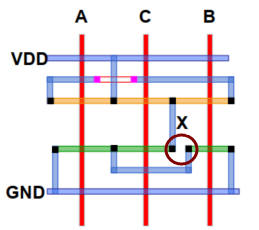

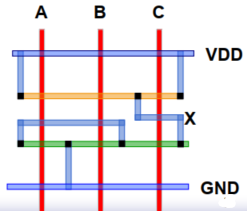

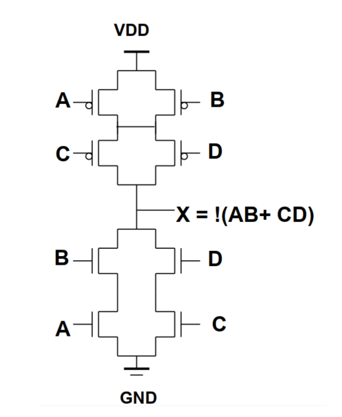

$eg:AOI22$

步骤一:画出逻辑图

步骤二:找出欧拉路径

步骤三:根据欧拉路径排布输入端顺序,并画出棍棒图

本博客所有文章除特别声明外,均采用 CC BY-SA 4.0 协议 ,转载请注明出处!