数字集成电路(7)传输管和传输门逻辑

本文最后更新于:2024年2月5日 晚上

本人《数字集成电路设计》课程笔记,老师为王仁平。

本文主要讲述静态互补CMOS电路中的传输管逻辑和传输门逻辑,其中传输门逻辑未整理成笔记。

第六章 CMOS组合逻辑门电路

6. 传输管逻辑

1. 有比逻辑

传输管逻辑是有比逻辑;互补CMOS是无比逻辑。

简单而言,

无比逻辑:输出的高低电平和尺寸无关。比如互补CMOS可以直接把输出电压拉到$V_{DD}$或者$GND$

有比逻辑:输出的高低电平和尺寸有关。基本没办法直接拉到最大逻辑摆幅。

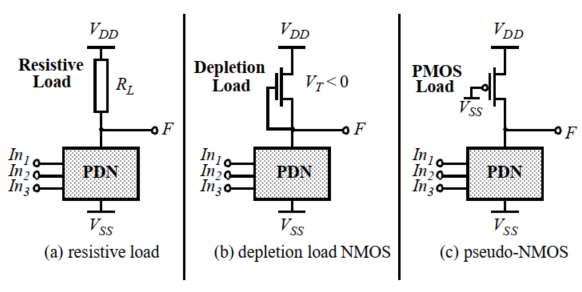

上拉网络由一个负载代替,如下三种常见的负载(电阻负载、有源负载、伪NMOS负载)

输出端的电压摆幅和门的功能取决于NMOS和PMOS的尺寸比

对于伪NMOS管负载

优点:逻辑门减小,面积减小,只需要$n+1$个管子,而互补CMOS需要$2n$个管子

缺点:

- 有比逻辑,达不到最大逻辑摆幅。

- 可能没办法完全关断MOS管,静态功耗增加。

应用:面积要求严格,性能要求不高的场景。

2. 传输管逻辑

1. 区别

传输管逻辑和互补CMOS有以下差别:

| 传输管 | 互补CMOS | |

|---|---|---|

| 逻辑 | 有比逻辑 | 无比逻辑 |

| 输入端 | 漏极D、栅极G |

只能栅极G |

| 面积/管子数/寄生电容 | 小/少/小 | 大/多/大 |

| 摆幅 | 存在$V_{TH}$,无法达到最大摆幅 | 可上拉到$V_{DD}$下拉到$GND$,实现最大摆幅 |

| 静态功耗 | 可能存在“关不断”情况,静态功耗较大 | 完全关断,静态功耗小 |

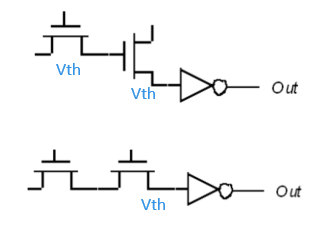

2. 串联

综合以上的区别,原因主要出在于输入端可以从D、G,而输出从S,从而使输出和输入之间存在$V_{TH}$的压降

为了减小$V_{TH}$带来的影响,传输管串联采用D-S-D-S的方式,而不采用D-S-G-S的方式

前者只有一个$V_{TH}$压降,而后者有两个

如下:

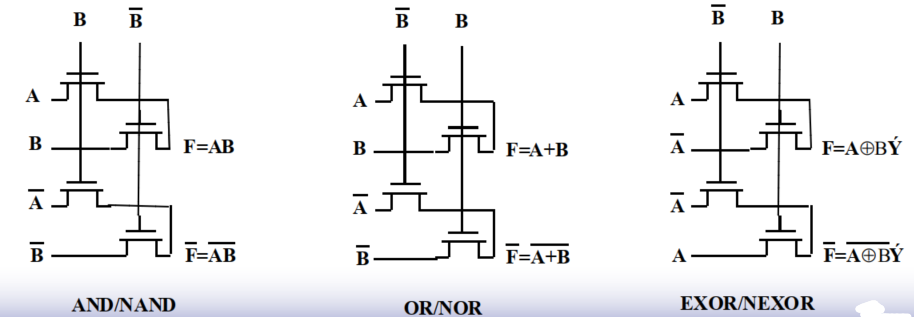

3. 互补传输管逻辑(CPL)

优点:

- 互补输入输出

- 每个输出节点都有一个低阻路径连接到$V_{DD}$或者$GND$

- 模块化

缺点:

存在$V_{TH}$,充电充不到$V_{DD}$,只能充到$V_{DD}-V_{TH}$

解决方法:电平恢复、多种阈值晶体管、传输门逻辑

确定输出:

以AND/NAND为例,

AND:$F=AB+B\overline{B}=AB$

NAND:$\overline{F}=\overline{A}B+\overline{B}·\overline{B}=\overline{AB}$

7. 传输门逻辑

笔者:时间有点久远,忘了为啥没写了

本博客所有文章除特别声明外,均采用 CC BY-SA 4.0 协议 ,转载请注明出处!