数字集成电路(11)时序报告

本文最后更新于:2022年10月19日 下午

本人《数字集成电路设计》课程笔记,老师为王仁平。

本文主要讲述如何查看时序报告。如何书写时序约束,可以参见《DC-lab4和lab6的略解》一文。

第七章 时序组合电路设计

3. 时序报告——求裕量slack

1. 建立时间

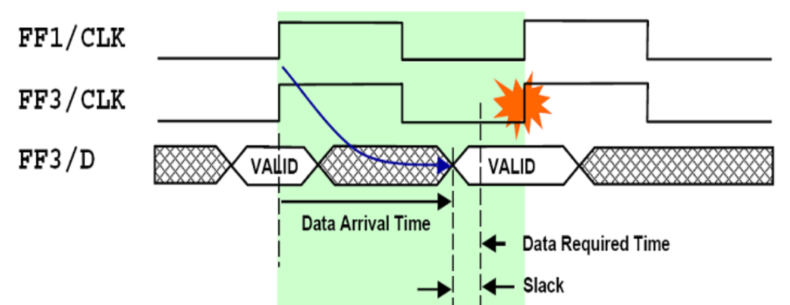

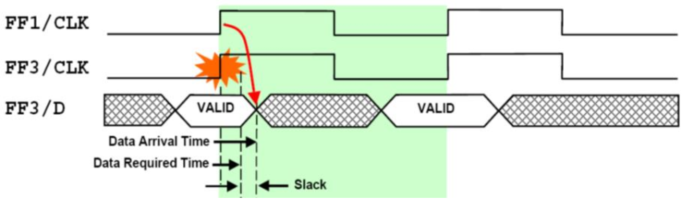

建立时间定义:对于捕获沿到来之前,数据需要保持稳定的最小时间

关于建立时间裕量$slack_{setup}$的定义,需要以下几个参数:

数据要求到达的时间——Date Required Time,令为$t_{date\ required}$

其中,

$T$:周期,如图整段的阴影部分

$t_{su}$:建立时间

数据实际到达的时间——Date Arrival Time,令为$t_{date\ arrival}$

其中,

$t_{c-q}$:寄存器的(最坏)传播延时

$t_{logic}$:两个寄存器之间组合逻辑的(最坏)传播延时

则有

为了充分考虑各种情况下,组合逻辑的建立时间裕量$slack_{setup}$,以下将分情况讨论。

在此之前,先明确几个概念:

- 理想时钟(ideal clock):以下的情况均不存在。

- 时钟偏差(clock skew):指同一个时钟域之间,时钟信号到达各个寄存器的最大时间差

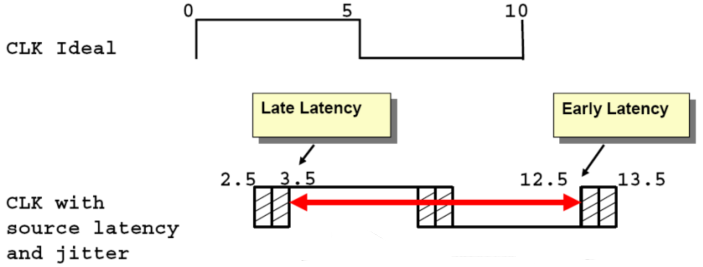

- 时钟抖动(clock jitter):芯片某一给定点上,时钟周期宽度发生变化,或缩短或变宽。一般我们会考虑最坏情况,具体见下文。

- (网络)时钟延迟(latency 或 network latency):外部时钟输入该模块后,时钟信号达到寄存器时钟输入端的延时。

- 源时钟延迟(source latency):从整个系统时钟源产生的时钟,到该模块时钟输入端的延时。

1. 理想时钟——ideal clock

指令:

1 | |

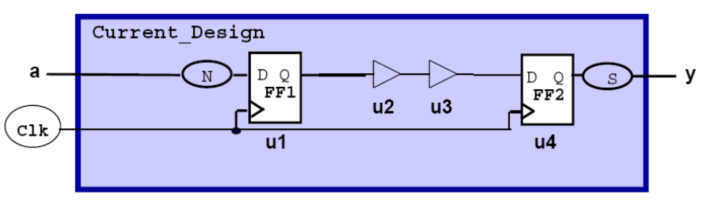

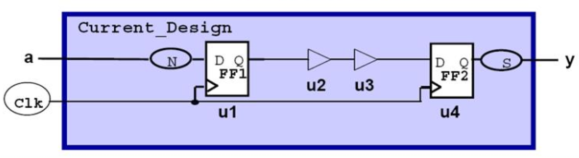

电路图:

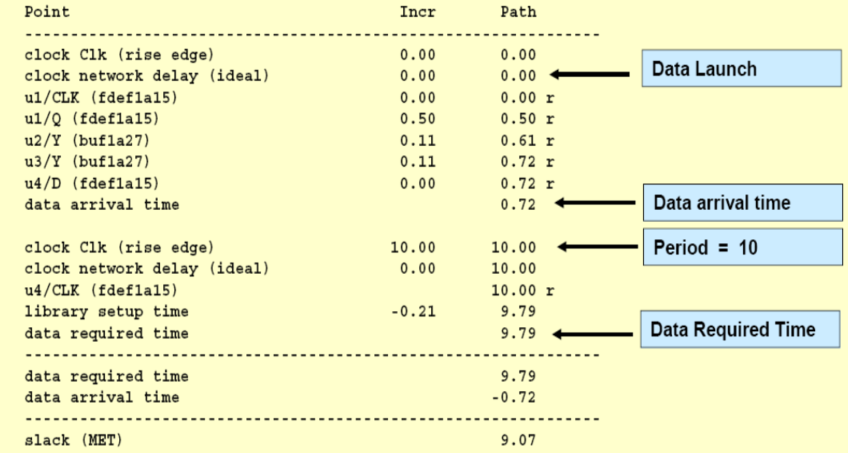

报告:

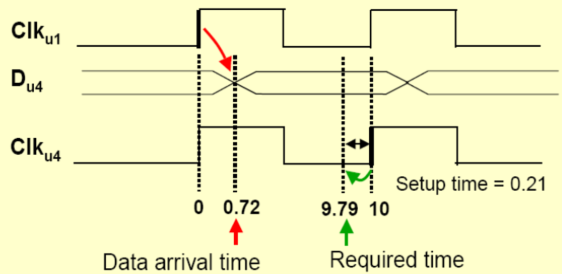

波形图:

根据公式$slack_{setup}=t_{date\ required}-t_{date\ arrival}$:

2. 时钟偏差——clock skew

指令:

1 | |

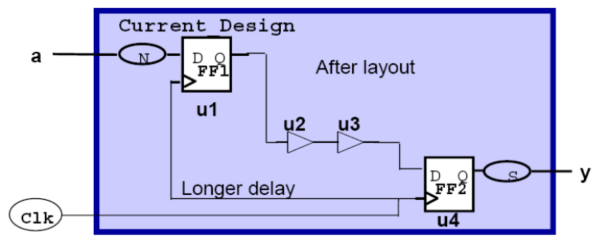

电路图:

报告:

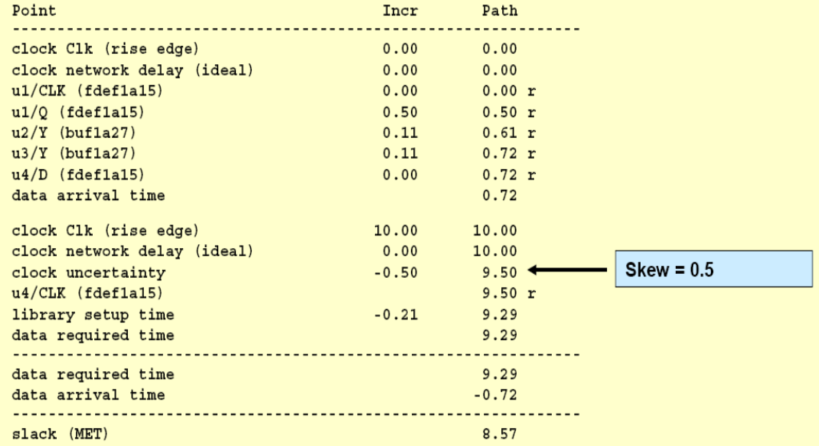

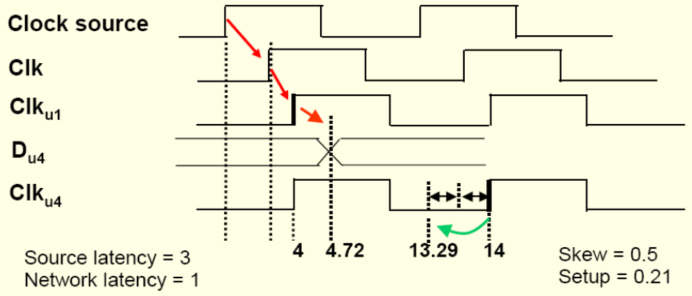

波形图:

可知,引入时钟偏差之后,(注意:因为负偏差对于建立时间不利,因此取$-t_{skew}$)

即,$t_{date\ required}=10-0.5-0.21=9.29$

因此,

小贴士:

和理想时钟相比,最坏情况下,捕获沿向前移动了$t_{skew}$,使得$t_{date\ required}$减小,从而减小了建立时间裕量。

3. 时钟网络延时——latency或network latency

代码:

1 | |

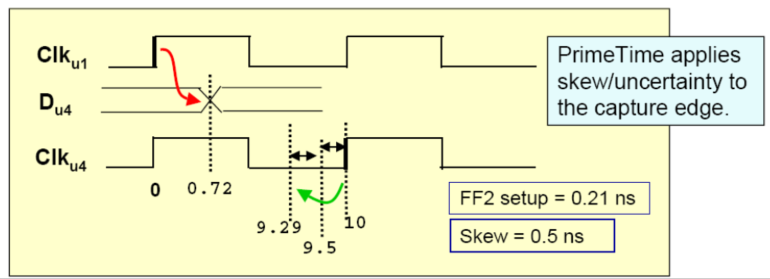

电路图:

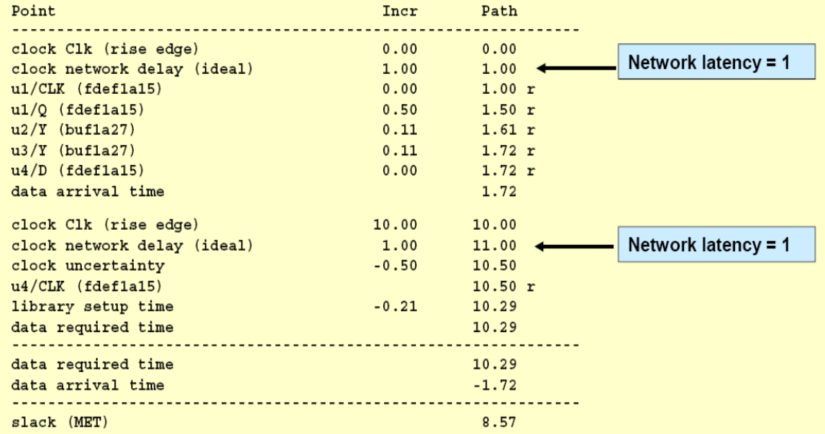

报告:

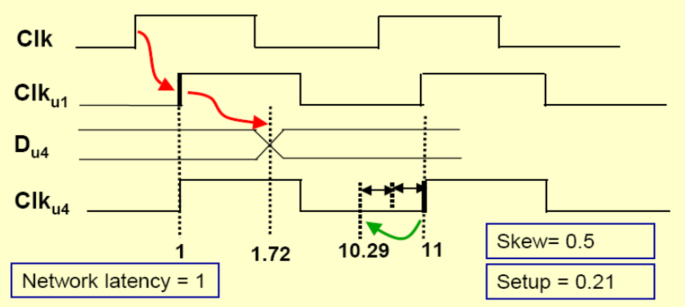

波形图:

引入时钟网络延时后,模块内的各个寄存器整体偏移了一个$t_{network\ latency}=1$

相比理想:

其中,$T-t_{skew}-t_{su}=10-0.5-0.21=9.29$,$t_{c-q}+t_{logic}=0.72$

因此,

小贴士:

和理想时钟相比,时钟网络延时是输入模块之后,时钟到寄存器时钟输入端的延时。

对于模块内的各个寄存器,相当于整体偏差了一个$t_{network\ latency}$

如时序报告所示,整体偏差了$t_{network\ latency}=1$

4. 源时钟延时——source latency

代码:

1 | |

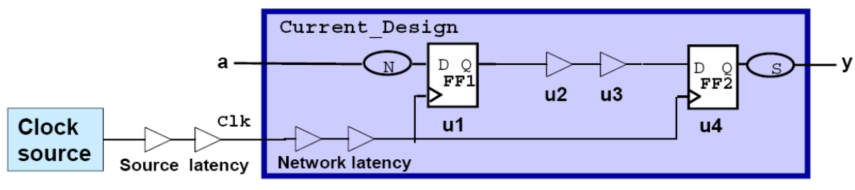

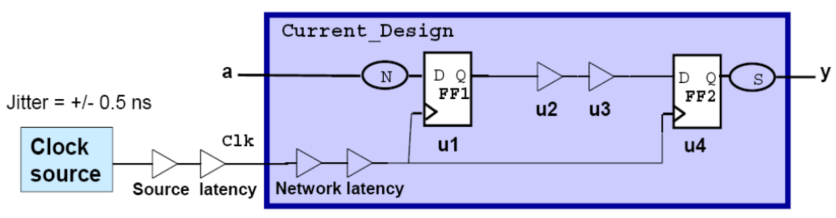

电路图:

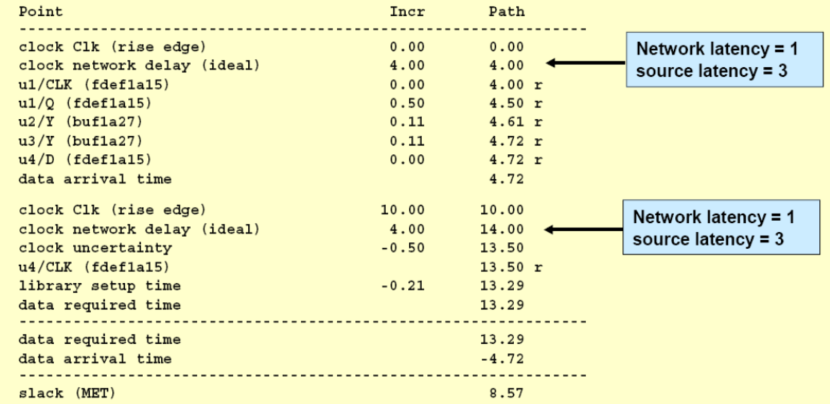

报告:

波形图:

引入源时钟延时后,输入模块的时钟同时钟源整体偏移一个$t_{source\ latency}=3$,也相当于模块内的各个寄存器整体偏移了一个$t_{source\ latency}=3$

相比理想:

其中,$T-t_{skew}+t_{network\ latency}-t_{su}=10-0.5+1-0.21=10.29$,$t_{c-q}+t_{logic}+t_{network\ latency}=0.72+1=1.72$

因此,

小贴士:

和理想时钟相比,引入源时钟延时后,输入模块的时钟同时钟源整体偏移一个$t_{source\ latency}=3$

也相当于模块内的各个寄存器整体偏移了一个$t_{source\ latency}=3$

对于模块内的各个寄存器,相当于整体偏差了一个$t_{source\ latency}$

如时序报告所示,整体偏差了$t_{source\ latency}=3$

5. 时钟抖动——clock jitter

代码:

1 | |

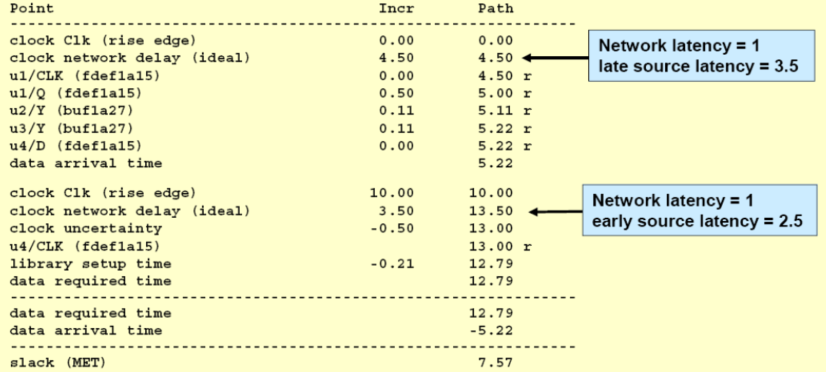

电路图:

报告:

波形图:

取最差情况——前一级时钟向后抖动,本级时钟向前抖动 ,如下图

最坏情况下,前一级时钟向后抖动0.5,本级时钟向前抖动0.5

因此,

其中,$T-t_{skew}+t_{network\ latency}-t_{su}=10-0.5+1-0.21=10.29$,$t_{c-q}+t_{logic}+t_{network\ latency}=0.72+1=1.72$

因此,

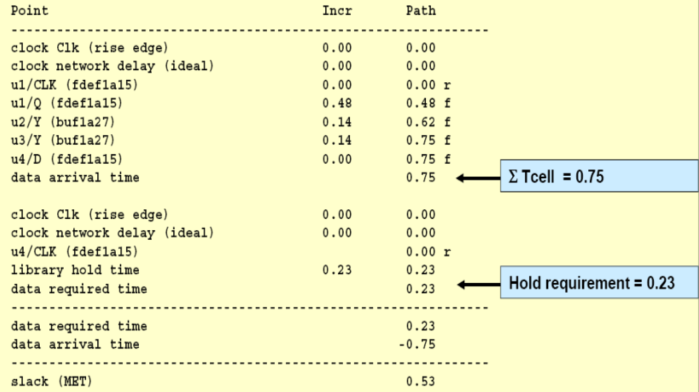

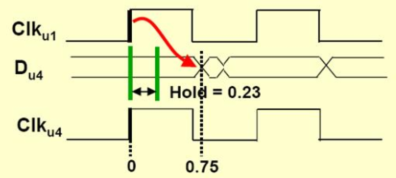

2. 保持时间

保持时间定义:对于捕获沿到来之后,数据需要保持稳定的最小时间

注意:保持时间看的是同一个时刻

同样的,对于保持时间裕度$slack_{hold}$,有

1.理想时钟——ideal clock

代码:

1 | |

电路图:

报告:

波形图:

注意:保持时间看的是同一个时刻,即同一时刻的$u_1$寄存器时钟和$u_4$寄存器时钟。

因此,

此处报告中,$slack_{hold}=0.53$应该是小数点近似的结果。

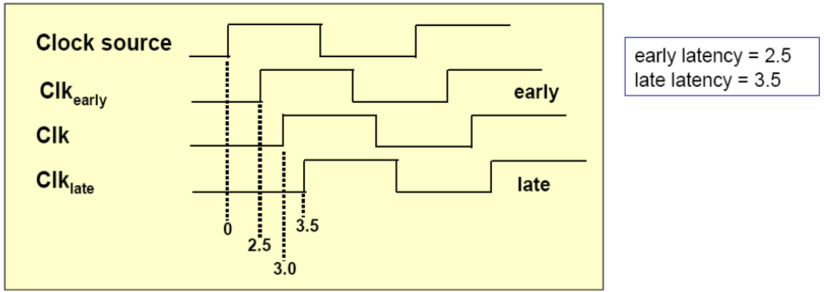

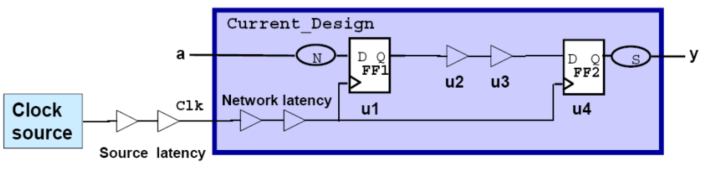

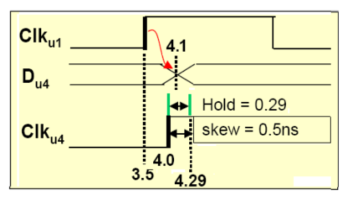

2. 源时钟延时、时钟网络延时——latency

代码:

1 | |

电路图:

波形图:

因为正偏差对于保持时间不利,故此使用的是$+t_{skew}$

因此,

本博客所有文章除特别声明外,均采用 CC BY-SA 4.0 协议 ,转载请注明出处!